- 全部

- 默认排序

很多消费类板卡的结构都是异形的,由专业的CAD结构工程师对其进行精准的设计,PCB布线工程师可以根据结构工程师提供的2D图(DWG或DXF格式)进行精准的导入操作,在PCB中定义板型结构。同时,对于一些工控板或者开发板,往往板框都是一个规则

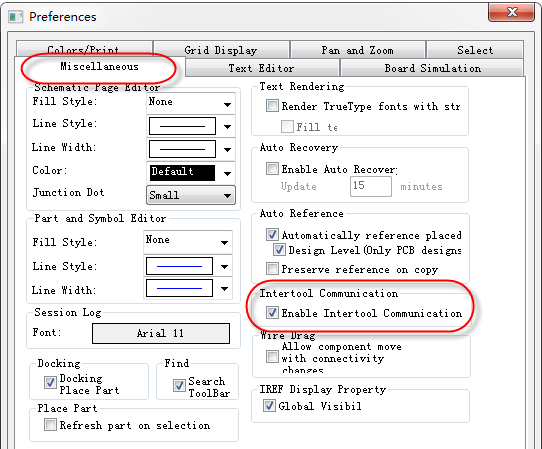

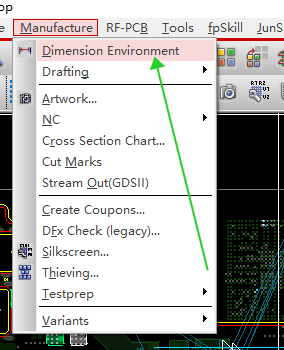

答:orcad与Cadence Allegro的交互式操作需要满足以下两个要求才可以实现:Orcad输出的是Allegro的第一方的网表,Allegro导入的是第一方网表,输出的具体方法见第3.35问;Orcad软件需要勾选以下选项,才可以实现交互式的操作,执行Options→Preference选项,选择Miscellaneous选项,如图3-71所示,在Intertoos Communication选项中,勾上下面的选项,才可以进行交互式操作; 图3-71 交互式操作示

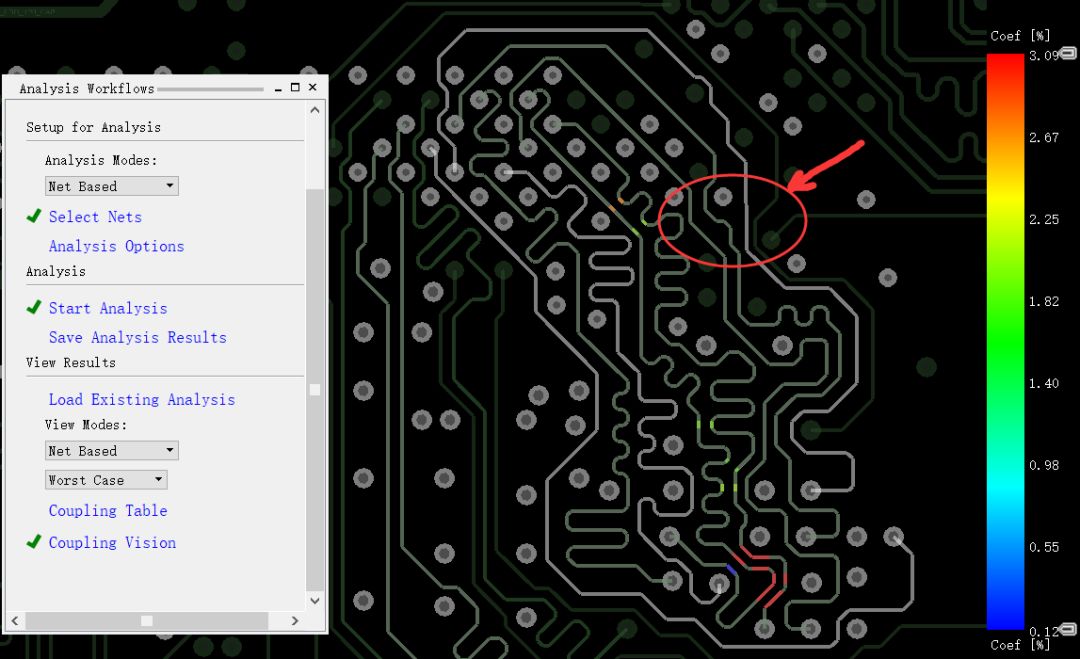

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。 PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。下面是在SigXplorer里面搭建了一个串扰的仿真链路,黄色部分就是得到的信号之间的串扰分析结果。

现在越来越多的高速设计是采用一种有利于加快开发周期的更有效的方法。先是建立一套满足设计性能指标的物理设计规择,通过这些规则来限制PCB布局布线。在器件安装之前,先进行仿真设计。在这种虚拟测试中,设计者可以对比设计指标来评估性能。而这些关键的前提因素是要建立一套针对性能指标的物理设计规则,而规则的基础又是建立在基于模型的仿真分析和准确预测电气特性之上的,所以不同阶段的仿真分析显得非常重要。

Cadence Allegro如何快速对齐器件 PCB设计过程中有一个环节是器件布局,器件的布局不但考虑电路的连通性,同时也考虑美观性,艺术性,所以器件布局尽可能整齐美观。 Allegro设计PCB过程中元件的对齐这要是通过栅格对齐的方式进行器件对齐,另一是用Align components对齐命令实现对齐的。 今天教大家如何使用“Align components”对齐命令快速对齐器件,操作方法如下:

扫码关注

扫码关注